We are the 3DEXPERIENCE company

First Quarter 2024 Results

Dassault Systèmes announces financial results for the first quarter 2024.

L&T Energy Hydrocarbon

Achieving sustainable growth in engineering, procurement and construction management.

Aerix Systems

To bring its omnidirectional unmanned aircraft system (UAS) to market, Aerix takes advantage of the Reinvent the Sky industry solution experience through the Startups program.

Accelerate R&D Productivity with a Digital Lab

Ready to reduce time to market? Take lab productivity to the next level with a game-changing scientific innovation platform.

Digitalize MedTech Manufacturing for Sustainable Operations

Embrace digitalization to create efficient, future-ready MedTech manufacturing.

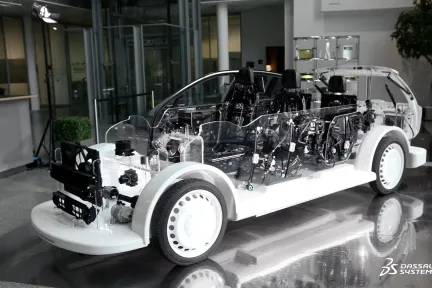

We Are the 3DEXPERIENCE Company

Our business is innovation. Through virtual universes, we help business and people create sustainable products and services to shape a better future.

Wherever You Are, Whatever You Are Doing, Dassault Systèmes Is There With You

Whether it’s developing smarter products that improve your daily life, transforming cities to be greener, or improving medical treatments, Dassault Systèmes drives innovation all around you.

MANUFACTURING INDUSTRIES

Reinventing manufacturing in the experience economy.

LIFE SCIENCES AND HEALTHCARE

Revolutionizing healthcare thanks to the power of virtual twins.

INFRASTRUCTURE & CITIES

Building today’s and tomorrow’s sustainable cities.

The 3DEXPERIENCE® platform

A Game-Changer for Business and Innovation

Bring together all aspects of your business in a single platform to increase collaboration, improve execution and accelerate innovation.

One Platform, Endless Possibilities

By combining a diversity of talents and breaking up the traditional silos, the 3DEXPERIENCE platform empowers organizations to invent, learn, produce, and trade in entirely new ways.

Transforming industries, markets and customer experiences

Every day, leading companies turn industry challenges into business opportunities thanks to the 3DEXPERIENCE platform. Our clients range from global industry leaders to startups, and even individuals.

Discover how Dassault Systèmes has helped companies in your industry to improve their products, boost their efficiency, and reduce costs.

Thousands of leading companies from all industries use our solutions. Find out why.

Hear from our customers to learn what made Dassault Systèmes the ideal choice for their businesses, and why we are the right partner for yours.

Explore our 3DEXPERIENCE portfolio and find the solution you’re looking for

Our portfolio comprises all stages of production, from design to delivery.

We provide 3D modeling and simulating applications.

We are experts in creating virtual twins of products and supply chains.

We revolutionize workflows thanks to our social, collaborative and information intelligence applications.

Dassault Systèmes supports all those who Imagine and Innovate

Today, we support more than 290,000 customers and 25 million users in 140 countries. Hear our clients tell their stories.

3DEXPERIENCE EDU

Reach a new milestone in your lifelong learning path.

Boost your employability and innovation power!

Training Services & Certification

Find the best training to upskill and reskill.

Need Support?

Search our knowledge base and engage with our communities to learn about products, services, and find the help you need.

Latest News

Read and listen to recent announcements in our newsroom.

Dassault Systèmes Events

We host and participate in events across the globe. Browse our events calendar to see where we’re going next.

Explore More About Us

Looking for something specific? Check out the links below.

Succeed with us

Get in touch.

Innovate with us

Create impact.

Grow with us

Build a sustainable future.